Technika cyfrowa. Przykładowe zadania.Bramki logiczne, układy kombinacyjne. Minimalizacja funkcji logicznych. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Linia długa i układy RC. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Algebra Boole’a, funkcje logiczne, postacie kanoniczne. 2.

Korzystając z praw de

Morgana podać formułę boolowską funkcji odwrotnych do: 3.

Napisać formułę

boolowską używając funkcji logicznych AND, OR i negacja opisującą funkcję

dwóch zmiennych x i y która przyjmuje wartość 1 wtedy i tylko wtedy kiedy

x=y. Podać tablicę prawdy funkcji. 4.

Zakładając, że x=x3x2x1

jest liczbą binarną 3 bitową opisać przy pomocy tablicy prawdy, postaci

kanonicznej sumy i postaci kanonicznej iloczynu funkcję logiczną która

przyjmuje wartość 1 kiedy: 5.

Opisać (tablica

prawdy, postacie kanoniczne) układ funkcji o dwóch argumentach A i B i dwóch

wartościach funkcji S i C który realizuje dodawanie binarne dwóch bitów Ai B.

Na wyjściu S powinna pojawiać się suma algebraiczna, a na wyjściu C

odpowiednie przeniesienie. 6.

Opisać układ 3 funkcji

logicznych realizujący dodawanie dwóch liczb 2 bitowych. 7.

Przedstawić funkcję w

skróconej postaci przy pomocy symboli mintermów (mi) 8.

Przedstawić funkcję w

skróconej postaci przy pomocy symboli maxtermów (Mi) 9.

Dla funkcji F i G

przedstaw tablicę prawdy funkcji F+G 10.

Rozważyć funkcję logiczną 5-ciu zmiennych przyjmującą

wartość 1 wtedy kiedy przynajmniej dwie zmienne są jedynkami. 11.

Dla zapewnienia w pomieszczeniu

odpowiednich warunków klimatycznych (temperatury i wilgotności) do

nagrzewania zastosowano grzejnik elektryczny, a do nawilżania nawilżacz. Przy

wilgotności<20% nawilżacz powinien działać, natomiast grzejnik powinien

wydzielać moc cieplną 10KW przy temp.<10 st.C, 8KW przy temp.=10-20 st. C,

2KW przy temp.>20 st.C. Natomiast przy wilgotności >20% nawilżacz

powinien być włączony tylko przy

temp.>20 st. C przy równoczesnym wyłączeniu grzejnika. Przy

niższych temp. nawilżacz powinien byc wyłączony a włączony grzejnik

wydzielający moc cieplna 8KW przy temp.<10^C, 2KW przy temp.=10-20 st.C. 12.

Funkcje

logiczne dwóch zmiennych: NAND, NOR, AND, OR, A’B, A’+B |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Bramki logiczne, układy kombinacyjne.

1.

Narysować układ kombinacyjny używając

bramek 2.

Narysować układ kombinacyjny używając

bramek AND, OR i NOT realizujący funkcję trzech zmiennych 3.

Zrealizuj funkcję AND korzystając z

trzech bramek NOR. 4.

Pokazać że: 5.

Narysować sieć logiczną bramek NAND

dla następujących formuł boolowskich: 6.

Narysować sieć logiczną bramek NOR dla

następujących formuł boolowskich: 7.

Dana jest funkcja podana w postaci

kanonicznej sumy: F(A,B,C,D) = A’BC+AD+AC. 8.

Zrealizować obwód złożony z kluczy który ma dwa

wejścia danych A i B, dwa wyjścia C i D oraz jedno wejście sterujące S. Dla

S=1 obwód ma łączyć A z C i B |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Minimalizacja funkcji logicznych.

1. Zminimalizuj

funkcję korzystając z przekształceń algebraicznych: 2. Używając

tablicy Karnaugh zminimalizuj formuły boolowskie: 3. Używając

tablicy Karnaugh zapisz funkcje w postaci minimalnej formuły boolowskiej

4. Używając

tablicy Karnaugh zapisz funkcje w postaci minimalnej formuły boolowskiej

5. Wyrażenie

(a) jest uproszczoną wersją wyrażenia (b). Znależć F* funkcji F.(użyj tablicy

Karnaugh) 6. Uprościć

wyrażenie: 7. Uprościć

wyrażenie opisane poniżej 8.

Możliwe jest

utworzenie więcej niż jednej postaci kanonicznej minimalnej dla danej

funkcji. Podać przykład takiej funkcji czterech argumentów dla której istnieją

przynajmniej dwie różne formuły boolowskie z taką sama ilością termów i

argumentów. 9.

Zminimalizować metodą

Karnaugh 10.

Zminimalizować metodą

Quinea-McCluskeya 11. Zminimalizować: 12.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Przerzutniki.

1.

Pokazać jak wykonać przerzutnik D

flip-flop z przerzutnika J-K. 2.

Pokazać jak wykonać przerzutnik T z

przerzutnika D. 3. W

oparciu o zwykły przerzutnik D flip-flop zbudować przerzutnik z wejściem

zerującym RESET i ustawiającym SET. 4. Sygnał

zegarowy dla przerzutnika może być generowany ręcznie poprzez cykliczne

przełączanie klucza z pozycji 0 na 1 i z powrotem. Jednak praktyczne kluczy

cechuje drganie zestyków (ang. bouncing) powodujące, że jedno przełączenie

wiąże się z przesłaniem ciągu impulsów. Zaproponuj układ oparty o przerzutnik

RS pozwalający na ręczne taktowanie zegara przy pomocy klucza pozwalający na

ominięcie tego problemu. 5.

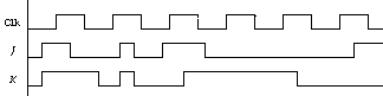

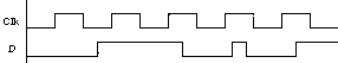

Dla przebiegu poniżej narysuj wyjście 6.

Przerzutnik RS może być zastosowany do

określenia które z wejść układu zostało uaktywnione jako pierwsze. Zbudować

układ o trzech wejściach i trzech wyjściach działający właśnie w ten sposób 7.

Narysuj przebieg na wyjściu przerzutnika: 8.

Obydwa wejścia przerzutnika JK są

sterowane przez funkcję Z=QÅX, gdzie X jest dodatkowym wejściem zewnętrznym. Narysuj przebieg

w węźle Z po podaniu na wejście sekwencji 01101010. Rozważyć dwa stany

początkowe przerzutnika 0 i 1. 9. Opierając

się na podstawowym schemacie przerzutnika JK-MS dorobić asynchroniczne

wejścia SET i RESET. 10. Dla przebiegów przedstawionych poniżej narysować wyjście

przerzutnika 11. Dla przebiegów przedstawionych poniżej narysować wyjście

przerzutnika 12. Zaprojektowano

kontroler dysku twardego pracujący z częstotliwością zegara 25MHz. Jednostka

centralna komputera z własnym zegarem przesyła komendy do sterownika co

200ns. Tak zbudowany system nie działa jednak dobrze. Co jakiś czas

„przewraca się” z powodu błędów w dostępie do pamięci dyskowej. Dlaczego tak

się dzieje? 13. Dokonaj konwersji przerzutników a)Przerzutnika XY na przerzutnik JK. Tablica przejścia

przerzutnika XY:

b)Przerzutnia MN na przerzutnik RS. Tablica przejścia

przerzutnika MN:

14. Przy pomocy przerzutnika JK zbuduj układ który działa w dwóch

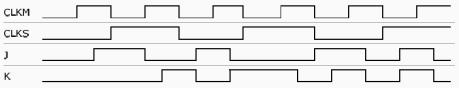

trybach: jak przerzutnik D lub jak przerzutnik T. 15. Narysować przebieg na wyjściu przerzutnika JK-MS przy założeniu,

że sekcja MASTER sterowana jest zegarem CLKM, a sekcja SLAVE zegarem CLKS |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Układy sekwencyjne.

1. Zaprojektować licznik przy użyciu przerzutników J-K zliczający w

dół od 5 do 0 i powtarza. Wykonać 2.

Powtórzyć poprzednie zadanie dla

przerzutnika D. 3.

Zaprojektować układ sekwencyjny

przechodzący kolejno przez podane stany: 4.

Zaprojektować układ sekwencyjny przechodzący kolejno przez podane

stany: 5.

Zaprojektować układ zapalający kolejno

8 diód w linijce diodowej. 6.

Zaprojektuj licznik modulo 4 (sekwencja

0,1,2,3) zliczający w dół lub w górę. Licznik posiada dodatkowo wejście

sterujące M. Kiedy M=0 licznik liczy w górę, dla M=1 licznik liczy w dół.

Użyj dowolnych przerzutników. 7.

Używając przerzutników J-K i

dodatkowych bramek logicznych zaprojektuj układ o wejściu X i wejściu Z.

Wyjście Z jest jeden tylko wtedy kiedy X było 1 przynajmniej przez 3 takty

zegara. Narysować diagram stanów, tablicę Karanugh dla wejść przerzutników i

schemat logiczny. 8.

Używając przerzutników J-K i

dodatkowych bramek logicznych zaprojektuj układ o dwóch wejściach X i Y, oraz

wyjściu Z. Wyjście Z jest jeden tylko wtedy kiedy X i Y są takie same

przynajmniej przez 3 takty zegara. W projekcie można wykorzystać układ zaprojektowany

w poprzednim zadaniu. 9. Zaprojektować koder szeroko stosowany np. w kodowaniu danych w

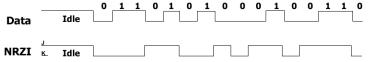

łączu szeregowym USB, koder NRZI. NRZI (ang. Non Return to Zero Inwert) to

sposób kodowania danych szeregowych w którym zera i jedynki są reprezentowane

przez ciągłe zmiany sygnału na linii danych. Stan sygnału ulega zmianie,

kiedy kodowany jest stan ‘0’. Kiedy Kodowane jest ‘1’ sygnał nie ulega

zmianie. 10. Zaprojektować licznik pierścieniowy o następującej sekwencji

stanów: 11. Dokonaj analizy pracy układu poniżej. Narysuj tablicę przejścia,

tablicę stanów i diagram stanów.

12. W

oparciu o układ licznika z kasowaniem (CLR), wejściem sterującym góra dół (U/D)

i wejściem zezwalającym EN przedstawionym poniżej oraz bramki logiczne

dokonać syntezy układu sekwencyjnego przedstawionego w tablicy.

Tablica

pracy licznika:

13. Zaprojektuj

układ sekwencyjny w oparciu o gotowy układ sekwencyjny przedstawiony w

tablicy

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Automaty.

1. Automat

Mealy’ego został zrealizowany przy użyciu 3 przerzutników, 2 wejść binarnych i

6 wyjść binarnych. 2.

Automat Moore’a został zrealizowany

przy użyciu 5 przerzutników, 3 wejść binarnych i 9 wyjść binarnych. 3. Dokonać

syntezy właściwej automatu szeregowej konwersji ciągu bitów w kodzie

naturalnym na kod U2. 4.

Dokonać syntezy właściwej automatu

szeregowo realizującego odejmowanie dwóch liczb podawanych na wejścia

automatu. 5. Dokonać syntezy właściwej automatu detekcji kierunku ruchu obrotowej

tarczy. Automat współpracuje z fotodetektorami rejestrującymi aktualne

położenie tarczy. Możliwe kombinacje

na wejściu automatu to 00

(obydwa detektory zasłonięte), 01, 10, 11. 6.

Zaprojektować automat o dwóch

wejściach binarnych. Automat porównuje kolejne stany na wejściach i wykrywa

sytuację w której równocześnie zmieniły się obydwa wejścia. 7.

Zaprojektować automat o jednym wejściu

i jednym wyjściu. Automat ustawia i pozostawia 1 na wyjściu kiedy

przynajmniej dwa zera , a następnie przynajmniej dwie jedynki pojawiły się na

wejściu. Narysuj diagram stanów automatu. 8.

Zaprojektuj automat o jednym

wejściu i jednym wyjściu binarnym taki, że układ ustawia na wyjściu 1 wtedy

kiedy całkowita ilość zer na wejściu jest podzielna przez 3, a ilość jedynek

jest parzysta. 9.

Zaprojektuj automat o jednym wejściu i

jednym wyjściu binarnym taki, że układ ustawia na wyjściu 1 wtedy kiedy

całkowita ilość zer na wejściu jest parzysta większa od 0, a ilość jedynek

jest nieparzysta. 10. Zaprojektuj układ o szeregowym wejściu 1 bitowym i wyjściu 2

bitowym wskazującym na wyjściu liczbę jedynak które wystąpiły na wejściu w

ostatnich 3 taktach. 11. Zaprojektuj układ o szeregowym wejściu 1 bitowym i szeregowym

wyjściu 1 bitowym. Wyjście automatu jest równe 1 ilekroć całkowita liczba

podanych dotychczas na wejście 0 jest parzysta, a liczba 1 jest nieparzysta i

większa od 1. 12. Zaprojektuj układ sterowania silnikiem podnoszącym i

opuszczającym bramę automatyczną. Układ powinien jako wejście przyjmować bit

sterujący P ( P=1- otwarcie bramy; P=0 – zamknięcie bramy) oraz bity stanu

wyłączników krańcowych bramy D i G (G=1 – brama w górze; D=1 – brama w dole).

Na wyjściu układ przyjmuje stany odpowiadające stanom pracy silnika: PODNOŚ,

OPUSZCZAJ i STOP. 13. Zaprojektować automat o jednym wejściu i jednym wyjściu.

Automat ustawia i pozostawia 1 na wyjściu kiedy kolejno przynajmniej dwa zera

, lub przynajmniej dwie jedynki pojawiły się na wejściu. Narysuj diagram

stanów automatu. 14. Zaprojektować

automat wykrywający na wejściu szeregowym sekwencję 1011. Sekwencje mogą się

nakładać. 15. Zaprojektować

automat szeregowego kontrolera parzystości. Automat analizuje kolejne 3

bitowe sekwencje. 16. Zaprojektować diagram stanu automatu o szeregowym wejściu

1-bitowym i szeregowym wyjściu 1-bitowym, który na wyjściu wystawia ‘1’ kiedy

różnica ilości zer i jedynek na wejściu jest podzielna przez 3. 17. Zaprojektować diagram stanu automatu o szeregowym wejściu

2-bitowym i szeregowym wyjściu 1-bitowym, który na wyjściu wystawia ‘1’ kiedy

suma liczb 2-bitowych na wejściu jest podzielna przez 3. 18. Zaprojektuj układ sekwencyjny sterujący drogową sygnalizacją

świetlną.

19. Dokonać syntezy automatu przedstawionego na grafie przy

pomocy układu licznika modulo 3 z wejściem zezwalajacym CE i sterowaniem

kierunku U/D |

||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||

|

|